DDR5 메모리 인터페이스에 효율적인 검증 및 디버깅

페이지 정보

본문

메모리 기술이 빠르게 발전하고 있는데, 측정 도구가 따라갈 수 있습니까?

5G는 빠르게 개발되고 있으며, 증강 현실과 인공 지능부터 클라우드 컴퓨팅 및 IoT까지 여러 가지 흥미로운 기술의 성장을 주도하고 있습니다.

해당 데이터를 모두 어딘가에 저장하고 그 어느 때보다 더 빠르게 액세스해야 합니다. 즉, DDR5 같은 기술이 여느 때보다 더 중요해졌습니다. DDR5는 대역폭과 밀도, 채널 효율성을 향상시킵니다.

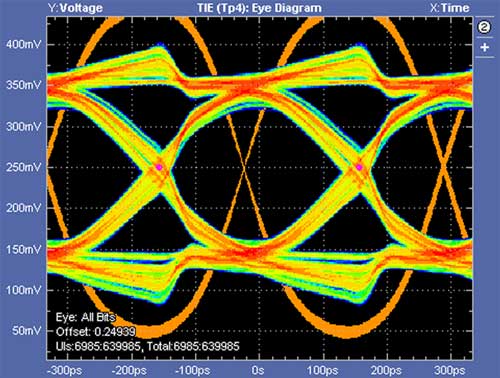

하지만, 데이터 전송률이 더 높고 신호 속도가 더 빠르다는 것은 신호 무결성의 가능성을 확장하고 컴플라이언스, 디버깅 및 검증에 대한 고성능의 측정 기능이 요구되는 복잡한 설계임을 뜻합니다.

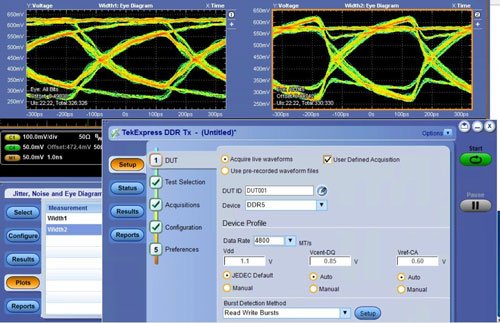

Tektronix TekExpress DDR5 송신기 솔루션은 JEDEC에서 정의한 50여 개의 전기/타이밍 측정을 충족하도록 DDR5 설계를 신속하고 효율적이며 안정적으로 검증 및 디버그할 수 있는 자동화된

시스템 레벨 테스트 애플리케이션입니다.

DFE 분석 ISI(기호 간 간섭)가 있는 상태에서는 최고의 DDR3/4 디버깅 툴을 사용하는 것만으로는 DDR5 설계를 테스트하기가 쉽지 않습니다. 텍트로닉스의 DDR5 시스템 레벨 컴플라이언스 소프트웨어는 다음과 같은 차세대 DDR에서 나타나는 문제를 해결할 수 있는 여러 가지 자동화된 툴을 제공합니다. 새로운 컴플라이언스 애플리케이션 아키텍처 | |

| 디버깅 및 검증 TekExpress DDR5 송신기 솔루션은 사용자와 함께 제어해야 하는 위치에 제어 기능을 배치합니다. 사용자 지정형 획득 모드를 이용하면 샘플링 속도, 레코드 길이, 대역폭 같은 스코프 설정을 사용자가 지정하여 DDR5 JEDEC 컴플라이언스 측정 작업을 실행할 수 있습니다. 텍트로닉스의 독립 실행형 DDR5 DFE 애플리케이션은 DFE 게인(gain)과 4개의 탭 값을 완전히 제어합니다. 이를 통해 JEDEC에서 정의하거나 규제하지 않는 자체 내부 테스트 계획을 실행할 수 있습니다. 또한 측정값의 상관관계를 시뮬레이션하여 시뮬레이션 모델을 미세하게 조정하고 4개의 탭과 게인 값을 변경해 가상 분석을 수행할 수 있습니다. |

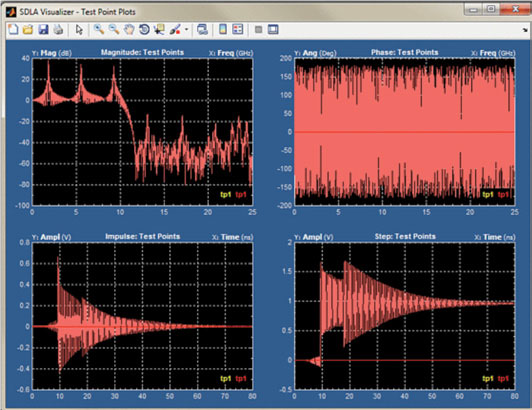

SDLA DDR5 설계를 디임베딩(de-embedding)하는 경우, S-파라미터를 검증하는 일이 주된 관심사 인 경우가 많습니다. 패시브 확인, 포트 할당 및 플로팅 기능이 향상된 SDLA(시리얼 데이터 링크 분석)는 S-파라미터 파일 검증 성능을 향상시켜 줄 뿐만 아니라 유연성을 개선하고 시간을 절약하며 제외 프로세스에 대한 신뢰도를 높여 줍니다. 전체 프로세스를 완료해 결과를 확인하려면 다른 디버그 소프트웨어 툴이 필요합니다. TekExpress DDR5 송신기 솔루션을 사용하면 초기 단계에서 문제를 감지해 더욱 효율적으로 설계를 디버그하며 최적화할 수 있습니다. 또한 SDLA 기능은 DFE 분석에도 유용할 수 있습니다. 자세한 내용은 여기에서 SDLA 앱 노트를 확인하십시오. | |

Featured Content |

|

|

| ||

DDR5 전기 검증 및 디버그 데이터 시트 | SDLA Visualizer(Serial Data Link Analysis Visualizer) | P7700 시리즈 TriMode 프로브 |

TekExpress DDR5 송신기 솔루션 소프트웨어에 대한 자세한 내용과 복잡한 DDR5 설계를 손쉽게 분석 및 최적화할 수 있는 방법을 알아보려면 이 데이터 시트를 확인하십시오. | SDLA Visualizer는 오실로스코프에서 직접 실행되는 완전한 측정 회로 소프트웨어로, 실시간 측정/시뮬레이션에 포함/제외된 필터를 계산해 주는 광범위한 기능을 제공합니다. 이 제품은 오실로스코프를 제어하고 이러한 필터를 사용해 실시간 파형을 만듭니다. | 팁 말단에서 아주 조금 떨어진 프로브의 입력 버퍼가 마운트된 솔더 다운 팁 같은 혁신적인 연결 기능을 갖춘 P7700 시리즈 Trimode 프로브는 오늘날 가장 까다로운 전기 설계에도 연결할 수 있는 탁월한 유용성을 제공합니다. |

| ||

DPO70000SX ATI 고성능 오실로스코프 | MSO/DPO70000 오실로스코프 |

|

DPO70000SX ATI 고성능 오실로스코프는 업계에서 가장 정확하게 고속 신호 동작을 캡처하여 차세대 설계를 확인, 검증 및 특성화할 수 있습니다. | 실제 신호를 확인하고 업계 최고의 파형 캡처 기능으로 더 많은 신호 세부 사항을 캡처할 수 있습니다. 더 빠른 설계 디버깅 및 컴플라이언스 테스트를 제공하도록 설계된 도구 집합으로 고속 시리얼 데이터 신호의 설정, 획득 및 분석을 자동화할 수 있습니다. |

|

- 이전글LPDDR5 메모리 인터페이스에 효율적인 검증 및 디버깅 21.05.17

- 다음글DDR 테스트, 검증 및 디버그 21.05.17

댓글목록

등록된 댓글이 없습니다.